Senior ASIC RTL Engineer, Core IP

Job Overview

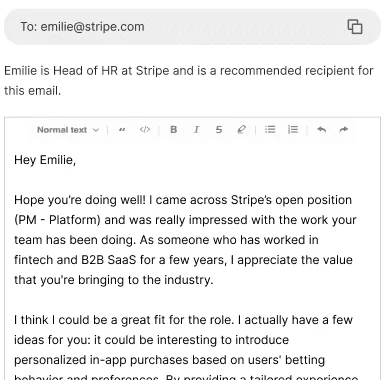

Who's the hiring manager?

Sign up to PitchMeAI to discover the hiring manager's details for this job. We will also write them an intro email for you.

Job Description

About the Role

Be part of a team that pushes boundaries, developing custom silicon solutions that power the future of Google's direct-to-consumer products. You'll contribute to the innovation behind products loved by millions worldwide. Your expertise will shape the next generation of hardware experiences, delivering unparalleled performance, efficiency, and integration.

The Platforms and Devices team encompasses Google's various computing software platforms across environments (desktop, mobile, applications), as well as our first party devices and services that combine the best of Google AI, software, and hardware. Teams across this area research, design, and develop new technologies to make our user's interaction with computing faster and more seamless, building innovative experiences for our users around the world.

Minimum Qualifications

- Bachelor's degree in Electrical Engineering, Computer Engineering, Computer Science, or a related field, or equivalent practical experience.

- 8 years of experience with digital logic design principles, RTL design concepts, and languages, such as Verilog or SystemVerilog.

- Experience with ASIC design methodologies and QA flows (Lint, CDC, RDC, VCLP), defining design constraints (SDC) and Low-power intent (UPF).

Preferred Qualifications

- Master's or PhD degree in Electrical Engineering, Computer Engineering or Computer Science.

- Experience with a scripting language like Perl or Python.

- Experience in design and development of audio blocks or Mobile Industry Processor Interface (MIPI) display or camera sub-systems.

Responsibilities

- Perform Verilog/SystemVerilog Register-Transfer Level (RTL) coding, functional/performance simulation debug and Lint/Cyber Defense Center (CDC)/VCLP checks.

- Participate in test planning and coverage analysis.

- Develop RTL implementations that meet engaged power, performance and area goals.

- Participate in synthesis, timing/power closure and support pre-silicon and post-silicon bring-up.

- Work with multi-disciplined and multi-site teams in Architecture, RTL design, verification, Design for Test (DFT) and Physical Design (PD).

Key skills/competency

- ASIC Design

- RTL Design

- Verilog

- SystemVerilog

- Digital Logic

- Power, Performance, Area (PPA)

- Synthesis

- Timing Closure

- Lint/CDC/VCLP

- Pre/Post-silicon Validation

How to Get Hired at Google

- Research Google's culture: Study their mission, values, recent news, and employee testimonials on LinkedIn and Glassdoor.

- Tailor your resume: Highlight ASIC design, RTL, Verilog, and power/performance optimization experience for this role.

- Showcase technical depth: Prepare to discuss digital logic, ASIC flows (Lint, CDC), SDC, and UPF in detail.

- Practice behavioral questions: Emphasize collaboration, problem-solving, and cross-functional teamwork aligned with Google's values.

- Network strategically: Connect with current Google hardware engineers on LinkedIn for insights and potential referrals.

Frequently Asked Questions

Find answers to common questions about this job opportunity

Explore similar opportunities that match your background