ASIC Design Verification Engineer, Machine Learning

Job Overview

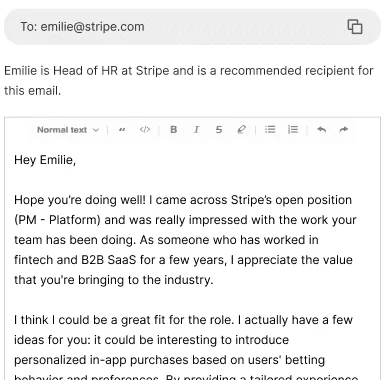

Who's the hiring manager?

Sign up to PitchMeAI to discover the hiring manager's details for this job. We will also write them an intro email for you.

Job Description

About the Role

In this crucial role as an ASIC Design Verification Engineer, Machine Learning at Google, you will be instrumental in shaping the future of AI/ML hardware acceleration. You'll have a unique opportunity to drive TPU (Tensor Processing Unit) technology that powers Google's most demanding AI/ML applications. Join a team that pushes boundaries, developing custom silicon solutions that power the future of Google's TPU. You'll contribute to the innovation behind products loved by millions worldwide, leveraging your design and verification expertise to verify complex digital designs, with a specific focus on TPU architecture and its integration within AI/ML-driven systems.

Minimum Qualifications

- Bachelor's degree in Electrical Engineering, Computer Engineering, Computer Science, or a related field, or equivalent practical experience.

- 4 years of experience with design verification.

- Experience with SystemVerilog/Verilog.

Preferred Qualifications

- Master's degree or PhD in Electrical Engineering, Computer Engineering or Computer Science, with an emphasis on computer architecture.

- 6 years of experience with silicon design verification.

- Experience contributing across the entire design and verification life cycle.

- Experience optimizing tools, flows, and methodologies to improve efficiency.

- Experience with scripting languages (e.g., Python or Perl).

- Excellent problem-solving and communication skills.

Responsibilities

- Plan the verification of complex digital design blocks by fully understanding the design specification and interacting with design engineers to identify important verification scenarios.

- Create and enhance constrained-random verification environments using SystemVerilog and UVM, or formally verify designs with SVA and industry leading formal tools.

- Identify and write all types of coverage measures for stimulus and corner-cases.

- Debug tests with design engineers to deliver functionally correct design blocks.

- Close coverage measures to identify verification holes and to show progress towards tape-out.

Key skills/competency

- ASIC Design Verification

- SystemVerilog

- UVM

- SVA

- Coverage Closure

- Debugging

- AI/ML Hardware

- Computer Architecture

- Python

- Perl

How to Get Hired at Google

- Research Google's culture: Study their mission, values, recent news, and employee testimonials on LinkedIn and Glassdoor.

- Tailor your resume for Google: Highlight ASIC verification, ML hardware expertise, and relevant projects showcasing SystemVerilog and UVM.

- Showcase SystemVerilog and UVM expertise: Be prepared to discuss your experience building constrained-random verification environments and applying formal verification.

- Prepare for technical interviews: Focus on ASIC design verification methodologies, debugging skills, computer architecture, and scripting languages like Python or Perl.

- Demonstrate problem-solving and collaboration: Be ready to share examples of how you've tackled complex verification challenges and worked effectively with design teams.

Frequently Asked Questions

Find answers to common questions about this job opportunity

Explore similar opportunities that match your background