Job Overview

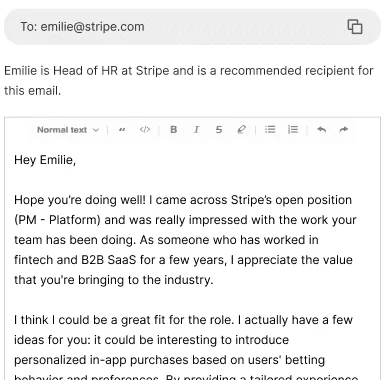

Who's the hiring manager?

Sign up to PitchMeAI to discover the hiring manager's details for this job. We will also write them an intro email for you.

Job Description

Summary

Do you love building elegant solutions to highly complex challenges? As part of our Silicon Technologies group, you’ll help design and manufacture our next-generation, high-performance, power-efficient processor, system-on-chip (SoC). You’ll ensure Apple products and services can seamlessly and efficiently handle the tasks that make them beloved by millions. Joining this group means you’ll be responsible for crafting and building the technology that fuels Apple’s devices. Together, you and your team will enable our customers to do all the things they love with their devices!

Description

The Front-End CAD Methodology Engineer plays a key role in promoting and driving robust, scalable methodology solutions across RTL Design and DV teams within Apple’s HWTech organization. This role leverages advanced automations and GenAI-driven capabilities to enhance engineering productivity, improve methodology quality, and enable intelligent workflow optimization across static verification, formal verification, simulation and emulation domains.

This position requires a combination of deep technical expertise, architectural vision, and technical leadership to identify high-impact opportunities, design and architect innovative solutions, including GenAI-enabled tooling, and drive adoption across a large globally distributed engineering organization. You will work closely with the different design organizations and CAD teams to translate complex engineering challenges into scalable, reusable, and forward-looking methodology solutions that accelerate silicon development and verification while maintaining the highest standards of quality and efficiency.

In short, this position focuses in fostering our North Star and making sure that our vision statement extends across the different design groups: To create, monitor, and maintain high quality flows that enable Apple Silicon to produce chips that enable Apple's best products.

You will be working with an energized and highly motivated CAD team that comprehensively supports Apple’s chip design efforts.

Minimum Qualifications

- Minimum of BS degree and 15+ years of relevant experience

- Experience with Front-End ASIC workflows

- Experience working directly with design and verification engineers to define requirements and implement solutions

- Experience with artificial intelligence and machine learning

Preferred Qualifications

- Experience debugging vendor tool problems

- Experience with Cadence or Synopsys’ static/formal/dynamic verification tools

- Experience with Python, TCL or Perl

- Experience with JSON or YAML

- Knowledge in Verilog and SystemVerilog; familiarity with VHDL

- Demonstrated experience driving large-scale software system development from specification to deployment

- Experience in implementing new functionality to solve emerging problems or to optimize already existing methods

- Great teammate with strong written and verbal interpersonal skills, and a service and support mentality

- Good communications skills are required and prior customer support experience

- MSEE/CE/CS preferred

Pay & Benefits

At Apple, base pay is one part of our total compensation package and is determined within a range. This provides the opportunity to progress as you grow and develop within a role. The base pay range for this role is between $212,000 and $386,300, and your base pay will depend on your skills, qualifications, experience, and location.

Apple employees also have the opportunity to become an Apple shareholder through participation in Apple’s discretionary employee stock programs. Apple employees are eligible for discretionary restricted stock unit awards, and can purchase Apple stock at a discount if voluntarily participating in Apple’s Employee Stock Purchase Plan. You’ll also receive benefits including: Comprehensive medical and dental coverage, retirement benefits, a range of discounted products and free services, and for formal education related to advancing your career at Apple, reimbursement for certain educational expenses — including tuition. Additionally, this role might be eligible for discretionary bonuses or commission payments as well as relocation. Learn more about Apple Benefits.

Note: Apple benefit, compensation and employee stock programs are subject to eligibility requirements and other terms of the applicable plan or program.

Apple is an equal opportunity employer that is committed to inclusion and diversity. We seek to promote equal opportunity for all applicants without regard to race, color, religion, sex, sexual orientation, gender identity, national origin, disability, Veteran status, or other legally protected characteristics. Learn more about your EEO rights as an applicant.

Apple accepts applications to this posting on an ongoing basis.

Key skills/competency

- Front-End ASIC workflows

- RTL Design

- DV teams methodology

- GenAI-driven automations

- Static/Formal/Dynamic Verification

- Python/TCL/Perl scripting

- Verilog/SystemVerilog

- Technical leadership

- Software system development

- Silicon development

How to Get Hired at Apple

- Research Apple's culture: Study their mission, values, recent news, and employee testimonials on LinkedIn and Glassdoor.

- Tailor your resume meticulously: Highlight your 15+ years of experience in front-end ASIC workflows, GenAI, and verification tools for this Front-End CAD Methodology Engineer role.

- Showcase technical depth: Emphasize expertise in Python, Verilog/SystemVerilog, and experience with Cadence/Synopsys tools.

- Prepare for behavioral interviews: Demonstrate strong communication, leadership, and problem-solving skills with specific examples relevant to large-scale silicon development.

- Network strategically: Connect with current Apple employees in Silicon Technologies or CAD teams on LinkedIn to gain insights.

Frequently Asked Questions

Find answers to common questions about this job opportunity

Explore similar opportunities that match your background