Staff Memory Subsystem RTL & Integration Engineer

AMD

Job Overview

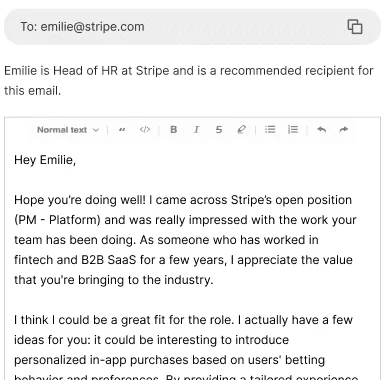

Who's the hiring manager?

Sign up to PitchMeAI to discover the hiring manager's details for this job. We will also write them an intro email for you.

Job Description

Staff Memory Subsystem RTL & Integration Engineer at AMD

At AMD, our mission is to build great products that accelerate next-generation computing experiences—from AI and data centers, to PCs, gaming and embedded systems. Grounded in a culture of innovation and collaboration, we believe real progress comes from bold ideas, human ingenuity and a shared passion to create something extraordinary. When you join AMD, you’ll discover the real differentiator is our culture. We push the limits of innovation to solve the world’s most important challenges—striving for execution excellence, while being direct, humble, collaborative, and inclusive of diverse perspectives. Join us as we shape the future of AI and beyond. Together, we advance your career.

The Role

The Memory Subsystem team at AMD is hiring a Senior Member of Technical Staff (SMTS) RTL and Integration Engineer to lead the definition, design, development, and integration of high-speed LPDDR/DDR memory subsystem solutions and associated IP. This role includes technical ownership of key memory subsystem components across multiple product lines and close collaboration with architecture, verification, firmware, BIOS, and physical design teams across geographically distributed sites.

The Person

You are a senior-level RTL and integration engineer with deep technical expertise and a system-level mindset. You are comfortable owning complex blocks or subsystems end to end, driving architecture discussions, and mentoring engineers through execution and debug.

Key Responsibilities

- Own and drive RTL design and integration for memory subsystem IP and top-level logic

- Lead micro-architecture definition and translate system requirements into robust RTL implementations

- Integrate IP blocks to deliver complete DDR/LPDDR memory subsystems across product lines

- Partner closely with verification teams on test strategy, debug, coverage, and pre-silicon issue resolution

- Collaborate with physical design teams on timing targets, floorplanning, CDC, and clocking strategies

- Drive resolution of complex functional, timing, and integration issues across subsystem boundaries

- Develop and maintain high-quality subsystem documentation, interface definitions, and timing diagrams

- Support pre-silicon and post-silicon bring-up and work with firmware and BIOS teams to enable features

- Mentor and technically guide other engineers, promoting best practices and design quality

Required Qualifications

- Expert proficiency in Verilog and SystemVerilog for RTL design

- Extensive experience designing and integrating IP and subsystems in complex SoC environments

- Strong understanding of memory subsystem architecture and micro-architecture

- Expert knowledge of clocking, resets, CDC, and synchronization techniques

- Proven ability to debug complex RTL and integration issues using simulation and emulation tools

- Experience leading technical efforts and collaborating across design, verification, firmware, and physical design teams

- Strong experience using Git and/or Perforce

Preferred Experience

- Hands-on experience with DDR/JEDEC standard IP, DDR PHY, memory controllers, or full memory subsystems

- Experience serving as technical owner for subsystem or major IP blocks

- Knowledge of SVA/OVL and synthesizable assertions

- Experience with VCS and Zebu emulation for debug and bring-up

- Strong understanding of power management, UPF, and low-power design techniques

- Experience analyzing system-level performance, power, and architectural tradeoffs

Academic Credentials

Bachelor’s or Master’s degree (or equivalent) in Electrical Engineering, Computer Engineering, Computer Science, or a related field, or equivalent practical experience.

Location

Ireland (Dublin or other AMD Ireland locations; hybrid working supported). Employment is contingent on meeting applicable export control and security requirements.

Key skills/competency

- RTL Design

- Memory Subsystem

- IP Integration

- Verilog

- SystemVerilog

- SoC Environments

- Clocking

- CDC (Clock Domain Crossing)

- Debugging

- Micro-architecture

How to Get Hired at AMD

- Research AMD's culture: Study their mission, values, recent news, and employee testimonials on LinkedIn and Glassdoor.

- Tailor your resume for memory subsystems: Highlight RTL design, Verilog, SystemVerilog, and SoC integration experience.

- Showcase problem-solving expertise: Prepare examples of complex debug and integration issue resolution.

- Prepare for technical depth: Expect questions on DDR/LPDDR architecture, clocking, resets, and CDC techniques.

- Demonstrate collaboration and leadership: Discuss experiences with cross-functional team engagement and technical mentoring.

Frequently Asked Questions

Find answers to common questions about this job opportunity

Explore similar opportunities that match your background